In August 2018, GlobalFoundries announced it was stopping development of 7 nm chips, citing cost. ASML Holding NV is their main supplier of EUV lithography machines. In May 2018, Samsung announced production of 7 nm (7LPP) chips this year.

In June 2018, the company announced mass production ramp up. In April 2018, TSMC announced volume production of 7 nm (CLN7FF, N7) chips. The company has not published any expected values for feature lengths at this process node. In February 2017, Intel announced Fab 42 in Chandler, Arizona will produce microprocessors using 7 nm (Intel 4 ) manufacturing process. In September 2016, GlobalFoundries announced trial production in the second half of 2017 and risk production in early 2018, with test chips already running. Also, their later generation 7 nm (N7FF+) production is planned to use EUV multiple patterning and to have an estimated transition from risk to volume manufacturing between 20. TSMC's 7 nm production plans, as of early 2017, were to use deep ultraviolet (DUV) immersion lithography initially on this process node (N7FF), and transition from risk to commercial volume manufacturing from Q2 2017 to Q2 2018. In April 2017, TSMC began risk production of 256 Mbit SRAM memory chips using a 7 nm (N7FF+) process, with extreme ultraviolet lithography (EUV). In April 2016, TSMC announced that 7 nm trial production would begin in the first half of 2017. Expected commercialization and technologies In June 2016, TSMC had produced 256 Mbit SRAM memory cells at their 7 nm process, with a cell area of 0.027 square micrometers (550 F 2) with reasonable risk production yields. In July 2015, IBM announced that they had built the first functional transistors with 7 nm technology, using a silicon-germanium process.

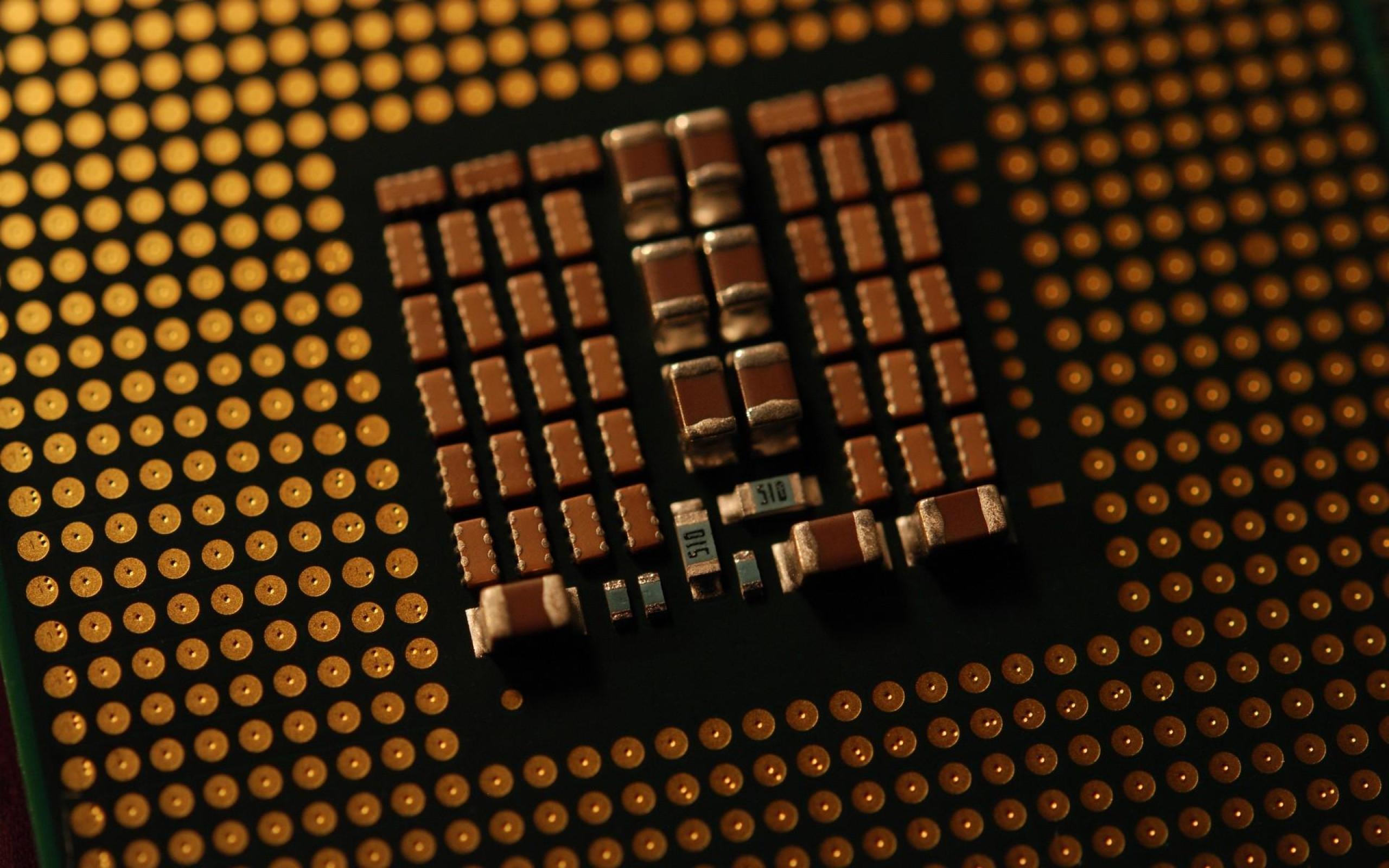

In 2003, NEC's research team led by Hitoshi Wakabayashi and Shigeharu Yamagami fabricated a 5 nm MOSFET. In 2002, an IBM research team including Bruce Doris, Omer Dokumaci, Meikei Ieong and Anda Mocuta fabricated a 6 nm silicon-on-insulator (SOI) MOSFET. ( November 2021)ħ nm scale MOSFETs were first demonstrated by researchers in the early 2000s. You can help by converting this section, if appropriate. This section is in list format but may read better as prose. TSMC and Samsung's 10 nm (10 LPE) processes are somewhere between Intel's 14 nm and 10 nm processes in transistor density. Since at least 1997, however, "node" has become a commercial name for marketing purposes that indicates new generations of process technologies, without any relation to gate length, metal pitch or gate pitch. The Radeon RX 5000 series is also based on TSMC's N7 process. However, the I/O die on the Rome multi-chip module (MCM) is fabricated with the GlobalFoundries' 14 nm (14HP) process, while the Matisse's I/O die uses the GlobalFoundries' 12 nm (12LP+) process. They also released their " Matisse" consumer desktop processors with up to 16 cores and 32 threads. In 2017, AMD released their " Rome" (EPYC 2) processors for servers and datacenters, which are based on TSMC's N7 node and feature up to 64 cores and 128 threads. Although Huawei announced its own 7 nm processor before the Apple A12 Bionic, the Kirin 980 on August 31, 2018, the Apple A12 Bionic was released for public, mass market use to consumers before the Kirin 980. The first mainstream 7 nm mobile processor intended for mass market use, the Apple A12 Bionic, was released at Apple's September 2018 event. Taiwan Semiconductor Manufacturing Company ( TSMC) began production of 256 Mbit SRAM memory chips using a 7 nm process called N7 in June 2016, before Samsung began mass production of their 7 nm process called 7LPP devices in 2018. It is based on FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology. In semiconductor manufacturing, the International Technology Roadmap for Semiconductors defines the 7 nm process as the MOSFET technology node following the 10 nm node.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed